ГОСТ Р 71289-2024

НАЦИОНАЛЬНЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

АРХИТЕКТУРА БАЗОВАЯ ПОСТРОЕНИЯ СИСТЕМ КОНТРОЛЬНО-ИЗМЕРИТЕЛЬНОЙ АППАРАТУРЫ PXIe

Технические требования

The basic architecture of PXIe test and measurement instrumentation systems. Technical specifications

ОКС 35.200

Дата введения 2024-04-01

Предисловие

1 РАЗРАБОТАН Обществом с ограниченной ответственностью "VXI-Системы" (ООО "VXI-Системы")

2 ВНЕСЕН Техническим комитетом по стандартизации ТК 019 "Электрические и электронные приборы"

3 УТВЕРЖДЕН И ВВЕДЕН В ДЕЙСТВИЕ Приказом Федерального агентства по техническому регулированию и метрологии от 11 марта 2024 г. № 295-ст

5 ВВЕДЕН ВПЕРВЫЕ

Правила применения настоящего стандарта установлены в статье 26 Федерального закона от 29 июня 2015 г. № 162-ФЗ "О стандартизации в Российской Федерации". Информация об изменениях к настоящему стандарту публикуется в ежегодном (по состоянию на 1 января текущего года) информационном указателе "Национальные стандарты", а официальный текст изменений и поправок - в ежемесячном информационном указателе "Национальные стандарты". В случае пересмотра (замены) или отмены настоящего стандарта соответствующее уведомление будет опубликовано в ближайшем выпуске ежемесячного информационного указателя "Национальные стандарты". Соответствующая информация, уведомление и тексты размещаются также в информационной системе общего пользования - на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет (www.rst.gov.ru)

Введение

Настоящий стандарт построен по принципу "сверху вниз", когда общие описания предшествуют более детальным, которые находятся далее в подразделах. Такая структура предназначена для удобства различных категорий пользователей: от разработчиков продуктов до системных интеграторов и конечных пользователей. Разработчики продуктов могут ознакомиться со всеми разделами настоящего стандарта, в то время как конечным пользователям может быть интересно только описание набора функций и, возможно, краткое изложение их реализации.

Настоящий стандарт содержит требования и разрешения, которые необходимо соблюдать всем разработчикам и поставщикам устройств на основе архитектуры PXI Express с учетом рекомендаций [1], [2]. Для полной реализации продуктов PXI Express необходимо руководствоваться указаниями настоящего стандарта (см. также [1] и [2]).

В настоящем стандарте приведено описание функциональных возможностей модулей и систем, построенных на базе архитектуры PXI Express, и способы их применения в контрольно-измерительных приложениях. Настоящий стандарт также устанавливает конструктивные, электрические и программные требования для реализации систем с архитектурой PXI Express.

Обзор архитектуры PXI Express

Архитектура PXI Express создана на основе архитектур построения модульных приборов и систем PXI-1 и CompactPCI Express, с целью достижения новых уровней производительности в модульных системах контрольно-измерительных приборов и автоматики (КИПиА). Аналогично архитектуре PXI-1, в PXI Express используются существующие отраслевые стандартные решения для получения преимущества высокой доступности компонентов при меньших затратах. PXI Express, также как и предшествующие архитектуры, продолжает поддерживать программную совместимость со стандартными персональными компьютерами, позволяя пользователям использовать знакомые программные инструменты и среды. PXI Express не только делает возможным значительное увеличение производительности измерений и автоматизации, но также обеспечивает высокий уровень совместимости с архитектурой PXI-1.

В PXI Express для передачи данных используются электрические сигналы широко распространенного интерфейса PCI Express. Это реализуется за счет соответствия модулей PXI Express соответствующим положениям (см. [1]), в которых, в свою очередь, электрические характеристики интерфейса PCI Express сочетаются с прочной механической конструкцией Eurocard и использованием высокоскоростных соединителей дифференциальных сигналов. Это позволяет системам измерения и автоматизации на базе PXI Express обеспечивать пропускную способность до 128 Гбайт/с в каждом направлении. PXI Express также сохраняет двустороннюю совместимость с продуктами CompactPCI Express.

Возможности работы с приборами в PXI Express выходят на новый уровень производительности за счет наличия дифференциальных сигналов триггерных событий "точка-точка", дифференциальных синхронизирующих сигналов тактовых импульсов и дифференциального системного тактового сигнала с частотой 100 МГц. Часто используемые в системах параллельная шина линий триггерных событий, линии триггерных событий "точка-точка" и тактовый сигнал 10 МГц (см. [2]) также сохранены. Это позволяет разработчикам модулей PXI Express находить оптимальные компромиссы между стоимостью и производительностью при реализации функций приборов.

PXI Express поддерживает совместимость с модулями, разработанными в соответствии с положениями [2], следующими способами:

1) PXI Express позволяет реализовывать в шасси инструментальные слоты, поддерживающие модули (см. [2]);

2) PXI Express вводит определение слота шасси, в который возможно устанавливать либо высокопроизводительный модуль, использующий PCI Express для передачи данных, либо модуль (см. [2]) с измененным соединителем. Это также обозначает, что PXI Express обеспечивает совместимость с модулями, разработанными с учетом соответствующих положений (см. [1]).

Системы PXI Express позволяют использовать большую базу существующего стандартного программного обеспечения. У пользователей персональных компьютеров (ПК) есть доступ к различным уровням программного обеспечения: от операционных систем и низкоуровневых драйверов до высокоуровневых драйверов приборов и программных библиотек. В системах PXI Express также задействуются все эти уровни программного обеспечения. Международный альянс производителей PXI систем предлагает отдельный стандарт на программное обеспечение для модулей, шасси и систем PXI Express (см. [3]). Отдельный стандарт на программное обеспечение позволяет быстрее внедрять в PXI Express системы поддержку новых операционных систем и стандартов программного обеспечения. При разработке модулей, шасси и систем PXI Express в соответствии с требованиями настоящего стандарта рекомендуется учитывать положения [3].

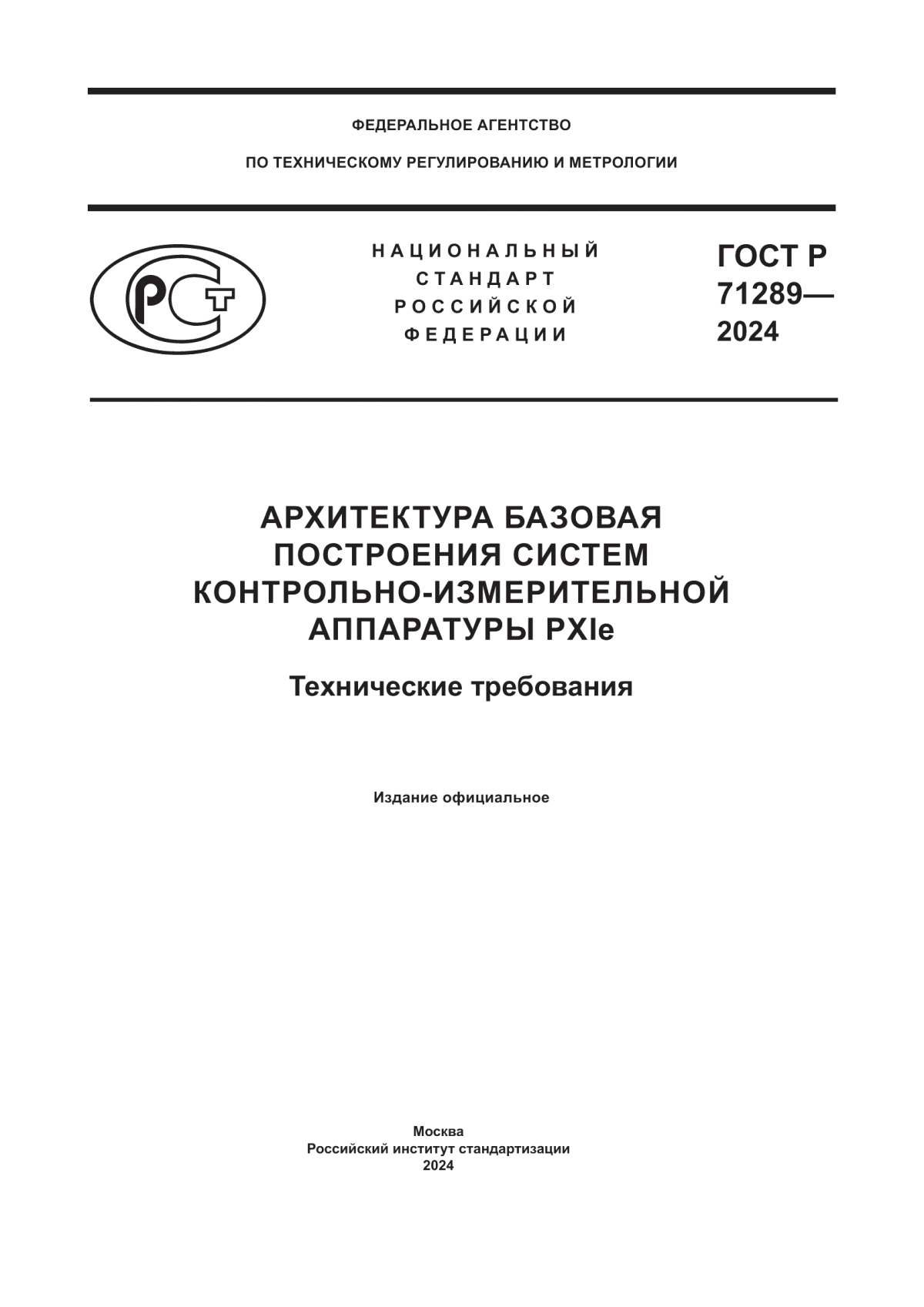

На рисунке 1 приведены основные свойства и функции PXI Express - уникальные и заимствованные из CompactPCI Express, а также свойства и функции, совместимые с предыдущими архитектурами PXI-1 и CompactPCI.

|

Рисунок 1 - Архитектура оборудования PXI Express

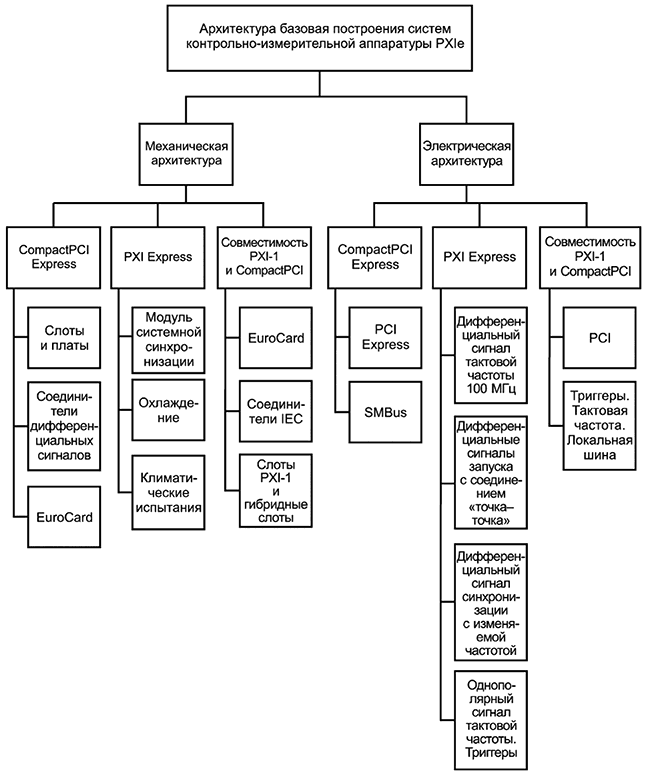

На рисунке 2 приведена архитектура программного обеспечения PXI Express (см. [3]).

|

Рисунок 2 - Архитектура программного обеспечения PXI Express

Структура стандарта

Настоящий стандарт устанавливает набор правил, рекомендаций, разрешений и замечаний наряду с поясняющим текстом, таблицами и рисунками. С целью четкого определения требований настоящего стандарта в его тексте применяют следующие ключевые слова:

- правило;

- рекомендация;

- разрешение;

- замечание.

Любой текст, не имеющий в качестве заголовков перечисленные ключевые слова, является описательной частью структуры системы или ее работы, изложенной в описательной или повествовательной форме.

Правила излагают основные требования настоящего стандарта, характеризующиеся словом "должно".

Соответствие данным правилам обеспечивает необходимый уровень совместимости оборудования различных производителей, ожидаемый системными интеграторами и конечными пользователями рынка контрольно-измерительной аппаратуры (КИА). Устройства, соответствующие настоящему стандарту, должны удовлетворять всем требованиям, изложенным в различных правилах.

Рекомендации обеспечивают дополнительное руководство, которое поможет производителям улучшить пользовательские характеристики устройств PXIe, характеризующиеся словом "следует". Следование рекомендациям улучшит функциональность, гибкость, совместимость и/или удобство использования устройств PXIe. Применение рекомендаций к устройствам не является обязательным.

Разрешения подчеркивают гибкость настоящего стандарта и характеризуются словом "могут". Разрешения главным образом разъясняют диапазон решений проектирования, который доступен проектировщикам модулей и систем на их усмотрение. Они позволяют проектировщикам манипулировать функциональностью, стоимостью и другими факторами для создания изделий, отвечающих ожиданиям пользователей. Разрешения носят нейтральный характер и не предполагают их обязательной реализации.

Замечания подчеркивают некоторые важные нюансы настоящего стандарта. Они помогают лучше понять подтекст некоторых требований настоящего стандарта и/или выделить главное из частных требований. Замечания в основном содержат советы по проектированию.

Все правила, рекомендации, разрешения и замечания должны рассматриваться совместно с сопутствующим текстом, таблицами и рисунками. Правила могут явно или неявно содержать информацию, приведенную в тексте, таблицах и рисунках. Несмотря на то, что настоящий стандарт и предполагает, что все необходимые требования изложены в правилах, возможно, что некоторые важные моменты оговариваются в настоящем стандарте за пределами правил. С точки зрения максимальной совместимости со стандартом, такие требования лучше трактовать как правила.

Успешная реализация устройств и систем PXIe требует знаний настоящего стандарта (см. также [1] и [2]).

1 Область применения

Настоящий стандарт распространяется на модульную контрольно-измерительную аппаратуру и устанавливает требования к разработке программно-аппаратных средств на основе архитектуры PXI Express.

Настоящий стандарт предназначен для решения следующих задач:

- обеспечения возможности гибкой конфигурации КИА для получения наилучшей производительности при эксплуатации;

- снижения стоимости разработки и внедрения КИА;

- снижения габаритных размеров контрольно-измерительных комплексов;

- повышения производительности модульных систем путем организации высокоскоростных потоков данных и тестовых сигналов;

- облегчения модификации КИА путем замены или дополнения модифицированных инструментальных модулей при сохранении неизменной структуры всей системы КИА;

- обеспечения возможности разработки систем с применением высокоскоростного интерфейса PCIe.

2 Нормативные ссылки

В настоящем стандарте использованы нормативные ссылки на следующие стандарты:

ГОСТ IEC 61010-1 Безопасность электрических контрольно-измерительных приборов и лабораторного оборудования. Часть 1. Общие требования

ГОСТ Р 53032 (ИСО 7779:1999) Шум машин. Измерение шума оборудования для информационных технологий и телекоммуникаций

ГОСТ Р МЭК 61326-1 Оборудование электрическое для измерения, управления и лабораторного применения. Требования электромагнитной совместимости. Часть 1. Общие требования

Примечание - При пользовании настоящим стандартом целесообразно проверить действие ссылочных стандартов в информационной системе общего пользования - на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет или по ежегодному информационному указателю "Национальные стандарты", который опубликован по состоянию на 1 января текущего года, и по выпускам ежемесячного информационного указателя "Национальные стандарты" за текущий год. Если заменен ссылочный стандарт, на который дана недатированная ссылка, то рекомендуется использовать действующую версию этого стандарта с учетом всех внесенных в данную версию изменений. Если заменен ссылочный стандарт, на который дана датированная ссылка, то рекомендуется использовать версию этого стандарта с указанным выше годом утверждения (принятия). Если после утверждения настоящего стандарта в ссылочный стандарт, на который дана датированная ссылка, внесено изменение, затрагивающее положение, на которое дана ссылка, то это положение рекомендуется применять без учета данного изменения. Если ссылочный стандарт отменен без замены, то положение, в котором дана ссылка на него, рекомендуется применять в части, не затрагивающей эту ссылку.

3 Термины и определения

В настоящем стандарте применены следующие термины с соответствующими определениями:

3.1 усовершенствованные дифференциальные соединители; ADF (advanced differential fabric): Дифференциальные высокочастотные соединители, используемые для передачи данных в модулях CompactPCI Express.

3.2 интерфейс прикладного программирования; API (application programming interface): Описание способов взаимодействия одной компьютерной программы с другими.

Примечание - Часто реализуется отдельной программной библиотекой или сервисом операционной системы. Используется программистами при написании всевозможных приложений.

3.3 системная шина CompactPCI Express: Системная шина передачи данных для контрольно-измерительной аппаратуры, являющаяся стандартом для разработки устройств на основе шины PCIe и соединителей типа Eurocard.

3.4 формат Eurocard (European packaging specifications): Стандартный конструктив исполнения печатных плат, предназначенных для размещения в специальных крейтах или шасси.

3.5 уведомление о технических [инженерных] изменениях; ECN (engineering change notice): Официальное уведомление об утверждении изменений, которое используют производители для того, чтобы убедиться, что их контрактные производства и другие партнеры-производители разрабатывают системы правильно.

3.6 электрически стираемое перепрограммируемое запоминающее устройство; EEPROM (electrically erasable programmable read-only memory): Один из видов энергонезависимой памяти.

3.7 усовершенствованный жесткий метрический разъем; eHM (enriched hard-metric): Специализированный соединитель ввода-вывода данных для печатных плат.

3.8 географический адрес; GA (geographical address): Шина, позволяющая однозначно определить положение модуля в шасси.

3.9 интерфейсная шина общего назначения; GPIB (general purpose interface bus): Параллельная шина передачи данных с кабелем и соединителем с 24 проводами, максимальная длина кабеля которых ограничена 20 м, выполненная по стандарту IEEE 488.

3.10 шина; ISA (industry standard architecture): 16-разрядная внутренняя шина компьютеров, основанных на процессорах Intel 80286 и их непосредственных преемниках в 1980-х годах.

3.11 выбор устройства инициализации; IDSEL (initialization device select): Сигнал формируется главным мостом или мостом PCI-PCI для выбора устройства при записи или чтении его памяти конфигурации.

3.12 интерфейс подключения периферийных устройств; PCI (peripheral component interconnect): Шина ввода-вывода данных для подключения периферийных устройств к материнской плате компьютера.

3.13 ускоренный интерфейс подключения периферийных устройств; PCI Express (peripheral component interconnect express): Локальная компьютерная шина расширения, предназначенная для подключения периферийных устройств к материнской плате персонального компьютера. Является высокоскоростной модификацией шины PCI.

Примечание - PCIe реализует программную модель интерфейса PCI и протокол последовательной передачи данных.

3.14 группа производителей PCI устройств; PCI-SIG (special interest group PCI): Задача группы состоит в развитии и управлении основанными на шине PCI стандартами передачи данных.

3.15 группа производителей промышленных компьютеров; PCI PICMG (PCI industrial computer manufacturers group): Группа для адаптации технологии PCI для использования в высокопроизводительных телекоммуникациях, военных и промышленных вычислительных приложениях, включая более новые технологии.

3.16 расширение PCI для контрольно-измерительных приборов; PXI (PCI extensions for instrumentation): Модульная система построения контрольно-измерительных приборов, основанная на шине PCI.

3.17 расширения PCI Express для контрольно-измерительных приборов; PXI Express (PCI express extensions for instrumentation): Модульная система построения контрольно-измерительных приборов, основанная на шине PCI Express.

3.18 модуль системной синхронизации; STM (system timing module): Модуль, обеспечивающий синхронизацию работы других модулей в системе.

3.19 слот системной синхронизации; STS (system timing slot): Специализированный слот для установки модуля системной синхронизации.

3.20 универсальный разъем питания; UPM (universal power): Специализированный разъем для электропитания платы.

3.21 архитектура программного обеспечения; VISA (virtual instrument software architecture): Широко используемый стандартизированный программный интерфейс в области тестирования и измерений для управления приборами с персонального компьютера.

3.22 универсальный стандарт Eurocard; VME (versa module Europe): Стандарт компьютерной шины VMEbus, первоначально разработанный для линейки процессоров Motorola 68000, но впоследствии широко используемый для многих приложений и стандартизован IEC как ANSI / IEEE 1014-1987.

Примечание - Стандарт основан на размерах, конструкции и соединителях Eurocard, но использует собственную систему сигнализации, которую Eurocard не определяет.

3.23 международная торговая ассоциация VMEbus; VITA (VMEbus international trade association): Некоммерческая бизнес-ассоциация, направленная на поддержку открытой системной архитектуры.

Примечание - Функции, выполняемые VITA, являются техническими, рекламными и связанными с пользователями, они направлены на увеличение общего размера рынка, предоставление поставщикам дополнительной информации на рынке и предоставление пользователям своевременной технической информации по всему миру.

3.24 спецификация VXIplug&play; VPP (VXIplug&play specification): Стандарт для разработки открытых систем VXI (см. 3.26).

3.25 организация по стандартизации VITA; VSO (VITA standards organization): Звено ассоциации VITA, направленное на решение вопросов по стандартизации.

3.26 расширения VME для приборов; VXI (VME extensions for instrumentation): Модульная система построения контрольно-измерительных приборов, основанная на шине VMEbus.

Примечание - VXI определяет дополнительные линии шины для синхронизации и запуска, а также требования к конструкции и стандартные протоколы для конфигурации, связи на основе сообщений, расширения нескольких шасси и других функций.

3.27 программируемая логическая интегральная схема; ПЛИС: Электронный компонент (интегральная микросхема), используемый для создания конфигурируемых цифровых электронных схем.

3.28 электромагнитная совместимость; ЭМС: Способность технических средств одновременно функционировать в реальных условиях эксплуатации с требуемым качеством при воздействии на них непреднамеренных электромагнитных помех и не создавать недопустимых электромагнитных помех другим техническим средствам.

3.29 форм-фактор: Стандарт технического изделия, описывающий некоторую совокупность его технических параметров.

3.30 слот: Посадочное место с группой соединителей, соединенных с системной шиной и ресурсами шасси, предназначенное для установки модуля.

3.31 триггерное событие: Изменение логического состояния сигнала, сигнализирующее о наступлении некоторого события, требующего реакции аппаратуры.

3.32 инструментальные сигналы: Сигналы, необходимые для обеспечения частотной и триггерной синхронизации периферийных модулей.

4 Общие сведения об архитектуре PXI Express

В данном разделе приводится обзор возможностей, конструкции, электрической и программной архитектур систем PXI Express, которым даются определения в настоящем стандарте.

4.1 Обзор конструкции

PXI Express, также как и PXI-1, поддерживает форм-факторы модулей 3U и 6U. Для поддержки PCI Express было добавлено несколько новых соединителей (см. [1]). В настоящем стандарте используются другие названия для модулей и типов слотов по сравнению с CompactPCI Express, а также вводятся некоторые новые понятия. В таблице 4.1 приведено наименование компонента PXI Express и эквивалентное наименование компонента CompactPCI Express.

Таблица 4.1 - Наименования в соответствии с настоящим стандартом и [1]

Наименование в настоящем стандарте | Наименование в [1] |

Системный слот PXI Express | Системный слот |

Системный модуль PXI Express | Системная плата |

Периферийный слот PXI Express | Периферийный слот типа 2 |

Периферийный модуль PXI Express | Периферийная плата типа 2 |

Гибридный слот PXI Express | Гибридный слот |

Модуль PXI-1, совместимый с гибридным слотом | Не применимо |

Слот синхронизации системы PXI Express | Не применимо |

Модуль синхронизации системы PXI Express | Не применимо |

Слот PXI-1 | Традиционный слот |

Модуль PXI-1 | Периферийная плата CompactPCI |

Типы модулей и слотов, определенные в [1], а также новые типы, представленные в настоящем стандарте, описаны в последующих разделах.

4.1.1 Типы модулей и слотов

В PXI Express определены следующие типы модулей и слотов: системный модуль PXI Express 3U и 6U и слот, периферийный модуль PXI Express 3U и 6U и слот, гибридный периферийный слот PXI Express 3U и 6U, модуль системной синхронизации PXI Express 3U и 6U и слот, гибридный слот 3U и 6U и модуль PXI-1, совместимый с гибридным слотом 3U и 6U. Помимо этих типов модулей и слотов в шасси PXI Express для реализации поддержки периферийных модулей PXI-1 разрешено использовать периферийные слоты PXI 3U и 6U (см. [2]).

4.1.1.1 Системные модули PXI Express 3U и 6U и слот

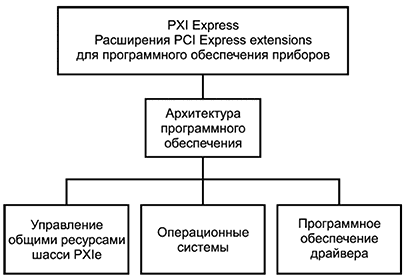

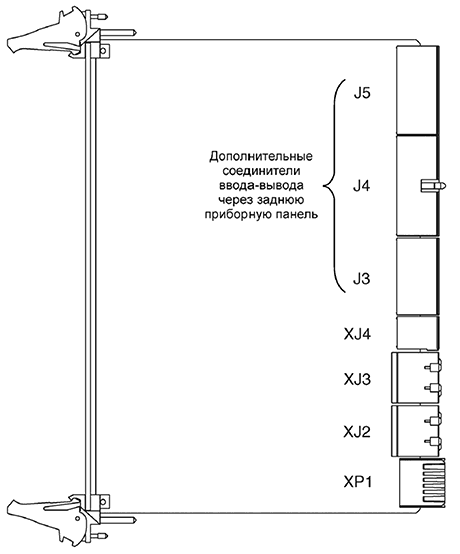

У системных модулей PXI Express имеется четыре обязательных соединителя: XP1/XJ2/XJ3/XJ4 (см. [1]). Упрощенное описание функциональности соединителей:

XP1/XJ1 предназначены для питания, XP2/XJ2 и XP3/XJ3 - для PCI Express, а XP4/XJ4 - для сигналов приборов (см. [2]). Системный модуль 6U может использовать соединители J3/J4/J5 для ввода-вывода через заднюю приборную панель.

На рисунках 4.1 и 4.2 показаны системные модули PXI Express 3U и 6U, соответственно.

|

Рисунок 4.1 - Системный модуль PXI Express 3U

|

Рисунок 4.2 - Системный модуль PXI Express 6U

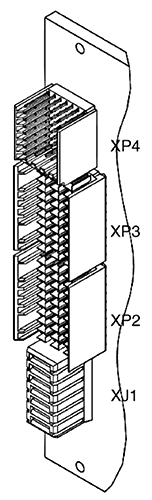

На рисунках 4.3 и 4.4 показаны системные слоты PXI Express 3U и 6U, соответственно.

|

Рисунок 4.3 - Системный слот PXI Express 3U

|

Рисунок 4.4 - Системный слот PXI Express 6U

4.1.1.2 Периферийный модуль PXI Express и слоты 3U и 6U

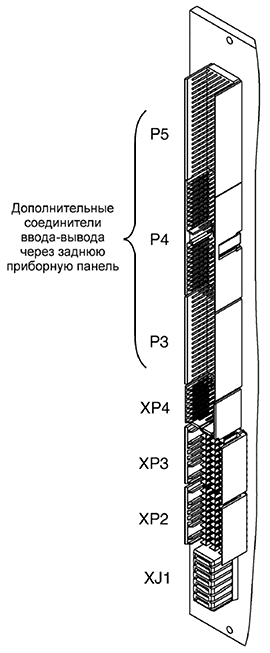

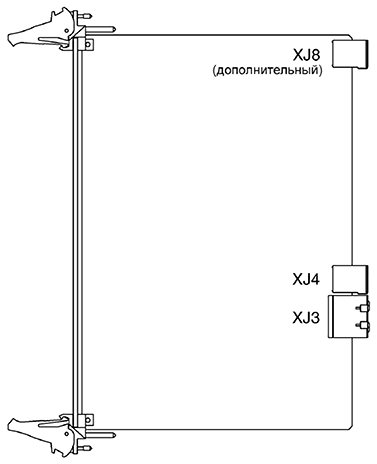

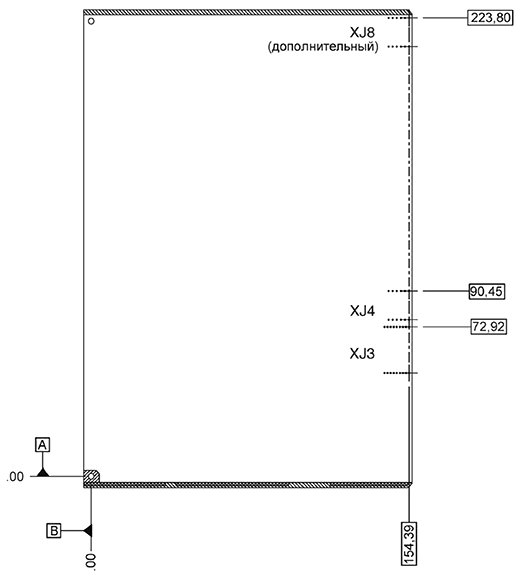

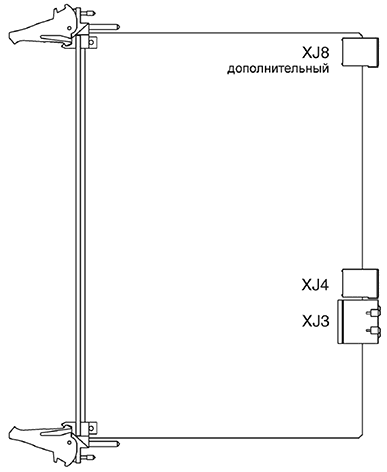

Периферийный модуль 3U PXI Express оснащен двумя соединителями: XJ3 и XJ4. Упрощенное описание функциональности соединителей: XP3/XJ3 предназначены для PCI Express и дифференциальных сигналов линий триггерных событий и синхронизации, а XP4/XJ4 - для сигналов измерительных приборов (см. [2]). Периферийный модуль 6U PXI Express имеет дополнительный соединитель eHM для кросс-плат и XJ8, который устанавливается в верхние колонки традиционного разъема J5 для обеспечения дополнительного питания модуля 6U. Настоящий стандарт не поддерживает использование J3/J4/J5 на периферийных модулях 6U.

На рисунках 4.5 и 4.6 показаны периферийные модули PXI Express 3U и 6U, соответственно.

Рисунок 4.5 - Периферийный модуль PXI Express 3U

|

Рисунок 4.6 - Периферийный модуль PXI Express 6U

На рисунках 4.7 и 4.8 показаны периферийные слоты PXI Express 3U и 6U, соответственно.

|

Рисунок 4.7 - Периферийный слот PXI Express 3U

|

Рисунок 4.8 - Периферийный слот PXI Express 6U

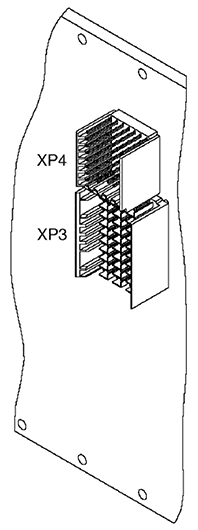

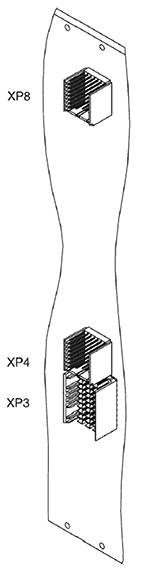

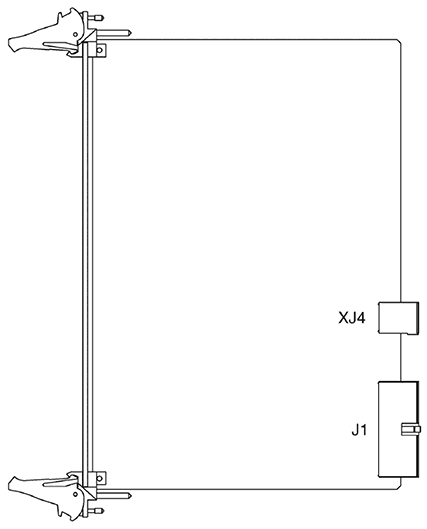

4.1.1.3 Гибридные периферийные слоты PXI Express 3U и 6U

Гибридные периферийные слоты 3U имеют три соединителя: P1, XP3 и XP4. Упрощенное описание функциональности соединителей: P1/J1 предназначены для 32-битного PCI, XP3/XJ3 - для PCI Express и дифференциальных сигналов триггерных событий и синхронизации, а XP4/XJ4 - для сигналов приборов (см. [2]). Гибридные периферийные слоты 6U оснащены четырьмя соединителями: P1, XP3, XP4 и XP8. Соединители P3, P4 и P5 не используются.

На рисунках 4.9 и 4.10 показаны гибридные слоты PXI Express 3U и 6U, соответственно.

|

Рисунок 4.9 - Гибридный периферийный слот PXI Express 3U

|

Рисунок 4.10 - Гибридный периферийный слот PXI Express 6U

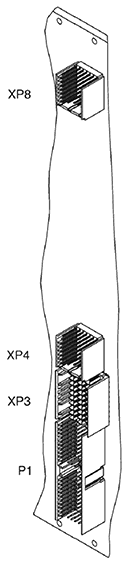

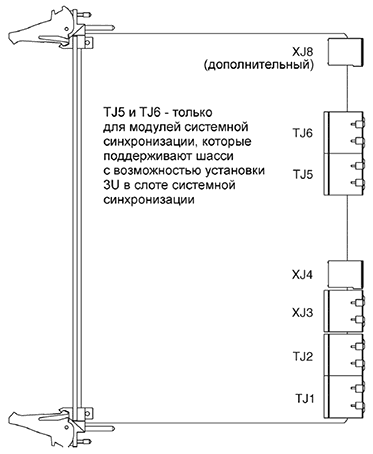

4.1.1.4 Модули системной синхронизации PXI Express 3U и 6U и слот

В PXI Express представлены новые модули 3U и 6U, называемые модулями системной синхронизации. Также представлены соответствующие слоты 3U и 6U, называемые слотами системной синхронизации (или слотами синхронизации системы).

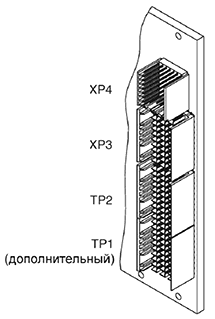

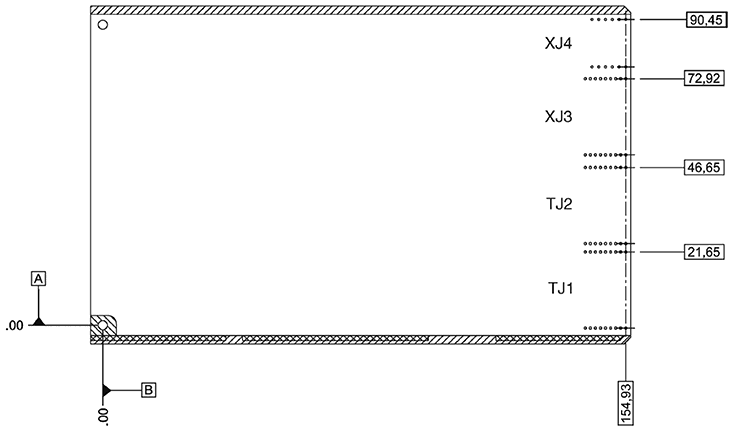

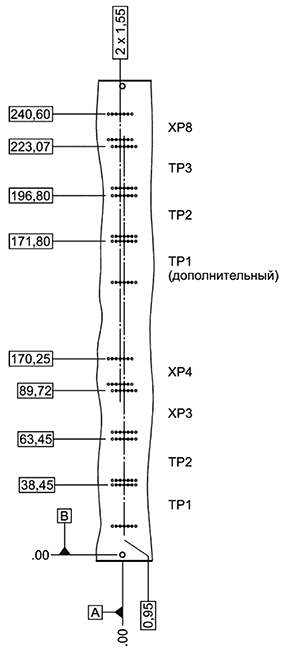

Модуль системной синхронизации 3U оснащен четырьмя соединителями: TJ1, TJ2, XJ3 и XJ4, как показано на рисунке 4.11. Упрощенное описание функциональности соединителей: TJ1/TP1 и TJ2/TP2 предназначены для разветвления линий дифференциальных сигналов триггерных событий и линий триггерных событий "точка-точка", XP3/XJ3 - для PCI Express и дифференциальных сигналов триггерных событий и синхронизации, а XP4/XJ4 - для сигналов приборов (см. [2]).

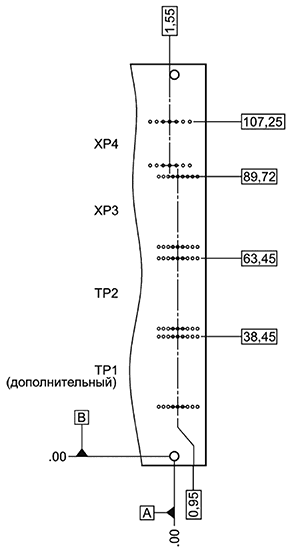

Слот 3U оснащен тремя необходимыми соединителями: TP2, XP3 и XP4. TP1 является необязательным для кросс-плат с семью или менее слотами, требующими линии дифференциальных сигналов триггерных событий.

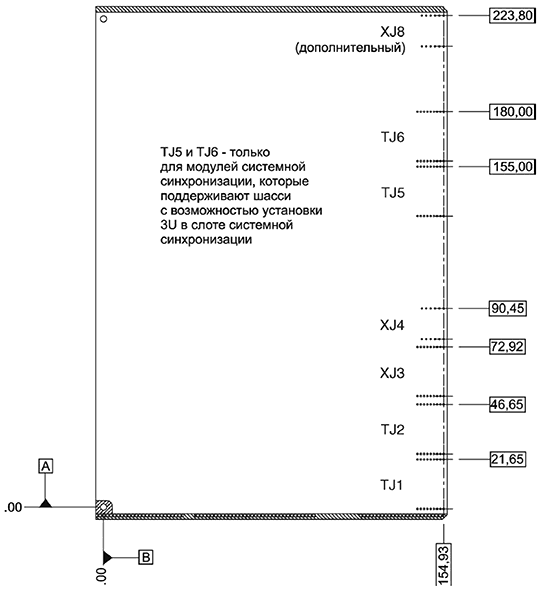

Модуль системной синхронизации 6U обладает теми же соединителями, что и модуль синхронизации 3U, а также дополнительным соединителем XJ8 для дополнительного питания.

Модуль системной синхронизации 6U, разработанный для шасси 6U, который поддерживает установку модулей 3U с более чем 18 слотами, оснащается дополнительными соединителями TJ5 и TJ6. Это позволяет модулю системной синхронизации 6U подключаться к дополнительным линиям триггерных событий.

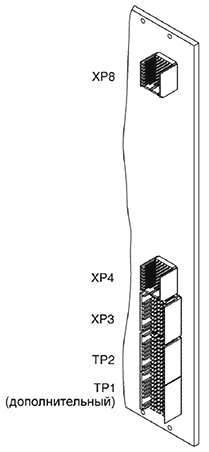

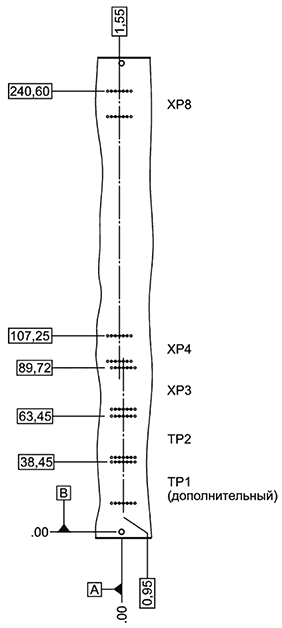

Слот системной синхронизации 6U, который не позволяет устанавливать модули системной синхронизации 3U, обладает четырьмя обязательными соединителями: TP2, XP3, XP4 и XP8. TP1 является необязательным для кросс-плат с семью или менее слотами, требующими линии дифференциальных сигналов триггерных событий.

Слот системной синхронизации 6U, поддерживающий установку модулей системной синхронизации 3U, оснащается семью необходимыми соединителями: TP1, TP2, XP3, XP4, верхний TP2, верхний XP3 и верхний XP4. Верхний соединитель TP1 является необязательным для кросс-плат с 24 или менее слотами, требующими линии дифференциальных сигналов триггерных событий.

|

Рисунок 4.11 - Модуль системной синхронизации PXI Express 6U

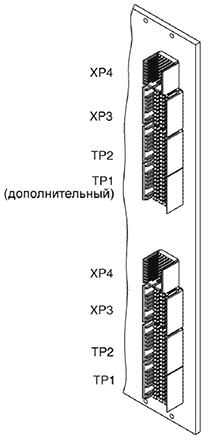

Слот системной синхронизации 3U PXI Express показан на рисунке 4.12.

|

Рисунок 4.12 - Слот системной синхронизации PXI Express 3U

Слот модуля системной синхронизации 6U показан на рисунках 4.13 и 4.14.

|

Рисунок 4.13 - Слот системной синхронизации PXI Express 6U

|

Рисунок 4.14 - Слот системной синхронизации 6U PXI Express с поддержкой установки 3U

4.1.1.5 Слот PXI-1

В шасси PXI Express могут быть слоты, поддерживающие платы PXI (см. [2]). Эти слоты соответствуют требованиям к конструкции с учетом положений [2] и называются слотами PXI-1.

4.1.1.6 Периферийный модуль PXI-1, совместимый с гибридными слотами 3U и 6U

PXI-1 или связанный с ним ECN определяет совместимый с гибридным слотом периферийный модуль PXI-1 3U и 6U, который является модулем PXI-1 3U или 6U, в котором соединитель J2 HM заменен на соединитель eHM. Соединитель eHM представляет собой модифицированный соединитель HM с шагом 2 мм со специальным позиционирующим ключом, который устанавливается в верхние восемь колонок соединителя J2 PXI-1. Этот тип модуля может использоваться в любом гибридном слоте PXI-1 или PXI Express. На рисунках 4.15 и 4.16 показаны модули PXI-1, совместимые с гибридными слотами 3U и 6U.

Рисунок 4.15 - Модуль PXI-1, совместимый с гибридным периферийным слотом 3U

|

Рисунок 4.16 - Модуль PXI-1, совместимый с гибридным периферийным слотом 6U

4.1.2 Расположение системного слота и модуля системной синхронизации

PXI Express определяет местоположение системного слота, как самый дальний левый слот в шасси с номером слота 1 (Slot 1). Это определенное расположение является подмножеством многочисленных возможных конфигураций, допускаемых положениями [1] (системный слот CompactPCI Express может быть расположен в любом месте на кросс-плате). Определение единого места для системного слота упрощает интеграцию и повышает степень совместимости между контроллерами PXI Express и шасси. Кроме того, требуется, чтобы при необходимости системный модуль расширялся влево до так называемых слотов расширения контроллера (см. [2]). Расширение влево не позволяет системным модулям использовать ценные периферийные слоты.

Некоторые шасси PXI Express могут интегрировать функциональные возможности системного модуля в шасси. В такой системе системный слот не требуется, а нумерация периферийных слотов начинается с 2.

PXI Express определяет слот системной синхронизации, в который может вставляться периферийный модуль PXI Express или модуль системной синхронизации, обеспечивающий индивидуальные триггеры для всех других периферийных модулей и позволяющий заменить системный опорный генератор. Расположение слота системной синхронизации не является обязательным, что позволяет разработчикам кросс-плат оптимизировать ее по стоимости.

4.1.3 Дополнительные конструктивные характеристики

В дополнение к функциям положений [2] в PXI Express добавлены дополнительные рекомендации по охлаждению, а также по измерению и характеристикам уровней акустического шума.

4.1.4 Совместимость с CompactPCI Express

Взаимодействие между продуктами, совместимыми с PXI Express, и стандартными продуктами CompactPCI Express является важной функцией, обеспечиваемой настоящим стандартом (см. также [1]). Для некоторых систем, совместимых с PXI Express, могут потребоваться компоненты, которые не реализуют специфические функции PXI Express. Например, пользователю может потребоваться использование стандартного модуля сетевого интерфейса CompactPCI Express в шасси PXI Express. Аналогичным образом, некоторые пользователи могут выбрать использование модуля, совместимого с PXI Express, в стандартном шасси CompactPCI Express. В таких случаях пользователь не сможет использовать специфические функции PXI Express, но сможет использовать базовые функции модуля.

Следует обратить внимание на то, что функциональная совместимость между продуктами PXI Express и другими реализациями продуктов CompactPCI Express для конкретных областей применения (которые могут определять другие назначения сигналов для контактов ввода-вывода соединителей XP4/XJ4) не гарантируется. Положения [1] оговаривают механические ключи соединителей XP4/XJ4 как для продуктов PXI Express, так и для продуктов CompactPCI Express для конкретных областей применения, чтобы исключить электрические конфликты между ними.

4.1.5 Типовые компоненты системы

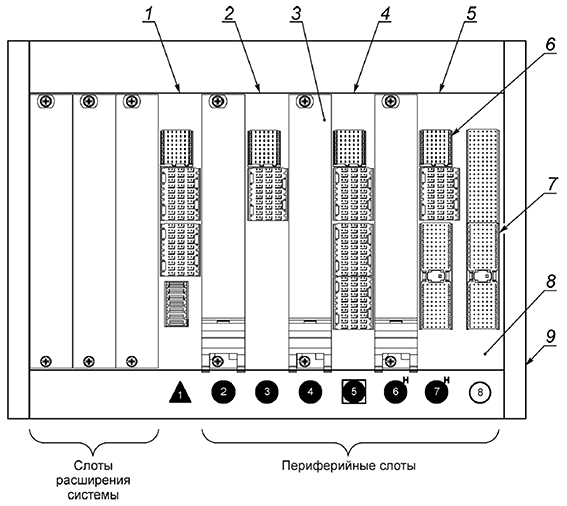

На рисунке 4.17 показан пример системы PXI Express для иллюстрации расположения основных компонентов системы. Система PXI Express состоит из шасси, которое содержит кросс-плату PXI Express и предоставляет средства для поддержки системного контроллера и периферийных модулей. Шасси может оснащаться одним системным слотом и должно содержать один или несколько периферийных слотов. Слева от системного слота может быть доступно любое количество слотов расширения системы. Слот системной синхронизации может располагаться в любом из доступных слотов справа от слота 1. Кросс-плата содержит интерфейсные соединители (XP1, XJ2 и т.д.) и обеспечивает связь между системным слотом, периферийными слотами и слотом синхронизации.

|

1 - системный слот PXI Express; 2 - периферийный слот PXI; 3 - модуль; 4 - слот синхронизации системы PXI Express; 5 - гибридный слот PXI Express; 6 - интерфейсные соединители кросс-платы; 7 - слот PXI-1; 8 - кросс-плата; 9 - шасси

Рисунок 4.17 - Типовые компоненты системы

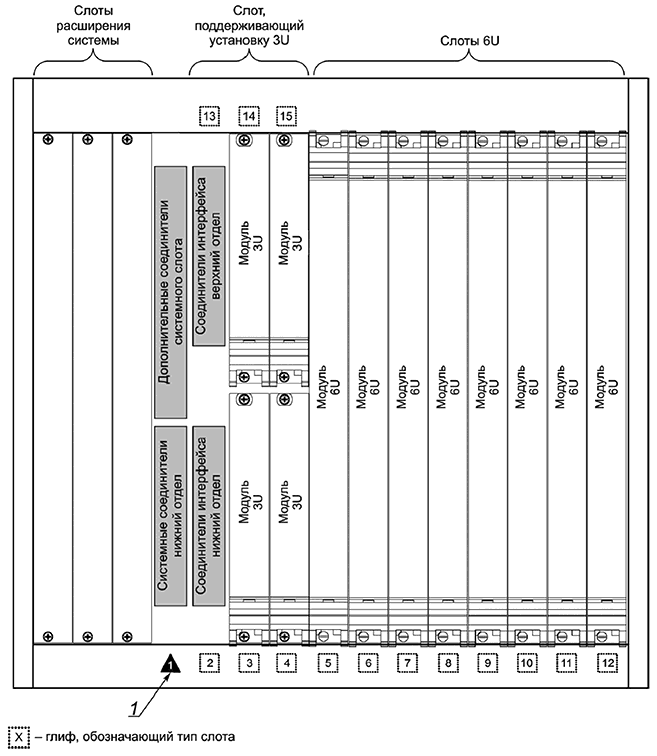

4.1.6 Шасси с поддержкой установки модулей 3U в слоте 6U

Так же, как и PXI-1, PXI Express позволяет эффективно использовать модули 3U в шасси 6U. Шасси 6U PXI Express может поддерживать установку определенных комбинаций модулей 3U в одном слоте 6U. Это позволяет одновременно вставлять один модуль 3U в нижнюю часть слота 6U, а другой модуль 3U - в верхнюю часть того же слота 6U. Это может быть реализовано механически с помощью адаптера 3U/3U или с помощью блочных каркасов. Шасси 6U PXI Express может быть выполнено с любым количеством слотов 6U, которые поддерживают эту функцию. На рисунке 4.18 показана общая конфигурация шасси 6U, поддерживающего установку модулей 3U.

|

1 - системный слот

Рисунок 4.18 - Пример шасси PXI Express с поддержкой установки 3U

4.2 Обзор электрической архитектуры

Подобно тому, как PXI объединил функции измерительных приборов со стандартом шины настольного компьютера PCI, PXI Express объединяет функции измерительных приборов со стандартом шины PCI Express, используемой в персональных компьютерах. Инструментальные функции PXI Express включают в себя многие инструментальные функции традиционного PXI, а также новый дифференциальный системный тактовый сигнал 100 МГц, новые двухточечные (связь типа "точка-точка") дифференциальные сигналы триггерных событий и новый двухточечный тактовый сигнал переменной частоты. Эти функции реализованы на кросс-плате для обеспечения максимальной производительности процессов тактирования и синхронизации инструментов.

4.2.1 Функции, заимствованные из CompactPCI Express

Интерфейс PCI Express - одна из основных функциональных возможностей, которую PXI Express заимствует у CompactPCI Express. Системы PXI Express могут передавать данные в системный модуль и из системного модуля со скоростью до 24 Гбайт/с в каждом направлении (при использовании 24 линии PCIe Gen 3), а отдельные периферийные модули PXI Express могут передавать данные со скоростью до 8 Гбайт/с в каждом направлении (при использовании 8 линий PCIe Gen 3). Учитывая, что коммутаторы PCI Express имеют возможность одновременной передачи данных между устройствами PCI Express по нескольким отдельным каналам, суммарная максимальная скорость передачи данных внутри системы PXI Express между всеми модулями может достигать 128 Гбайт/с в каждом направлении. Величина пропускной способности системы зависит от конкретной реализации и позволяет поставщикам PXI Express разрабатывать системы, отвечающие потребностям клиентов с точки зрения стоимости и производительности.

Электрические правила, перенесенные из положений [1] в PXI Express, оговаривают следующие аспекты (но не ограничиваются ими):

- ресурсы для передачи и приема электрических сигналов PCI Express;

- опорный тактовый генератор PCI Express;

- вспомогательные сигналы PCI Express;

- шину SMBus;

- идентификацию кросс-платы и ее возможностей через SMBus;

- сигналы, используемые для управления питанием;

- требования к источнику питания;

- назначение выводов модулей и слотов, за исключением дополнительных измерительных сигналов;

- использование интерфейса PCI с определенными типами слотов.

В таблице 4.2 показаны компоненты, совместимые между двумя стандартами. Следует обратить внимание на то, что если модули PXI Express используются в шасси CompactPCI Express, то инструментальные функции модулей PXI Express недоступны для использования.

Таблица 4.2 - Совместимость компонентов PXI, PXI Express и CompactPCI Express

Компоненты | Компоненты CompactPCI Express | ||||||

PXI Express | Систе- мный слот | Систе- мная плата | Перифе- рийный слот типа 2 | Перифе- рийная плата типа 2 | Гибрид- ный слот | Традици- онный слот CompactPCI | Перифе- рийная плата CompactPCI |

Системный слот PXI Express | - | Да | - | - | - | - | - |

Системный модуль PXI Express | Да | - | - | - | - | - | - |

Периферийный слот PXI Express | - | - | - | Да | - | - | - |

Периферийный модуль PXI Express | - | - | Да | - | Да | - | - |

Гибридный слот PXI Express | - | - | - | Да | - | - | Да |

Модуль PXI-1, совместимый с гибридным слотом | - | - | - | - | Да | Да | - |

Слот системной синхронизации | - | - | - | Да | - | - | - |

Модуль системной синхронизации | - | - | Да | - | - | - | - |

Слот PXI-1 | - | - | - | - | - | - | Да |

Модуль PXI-1 | - | - | - | - | - | Да | - |

Периферийная плата CompactPCI будет работать, если на ней имеется только соединитель J1. | |||||||

4.2.2 Функции, заимствованные из PXI

Продукты PXI Express могут пользоваться преимуществом повышения производительности работы с данными при реализации функций приборов (см. [2]). В дополнение к новым функциям приборов, определенным в настоящем стандарте, любой модуль PXI Express и слот шасси могут задействовать системную тактовую частоту (тактовый генератор) PXI 10 МГц (PXI_CLK10), шину линий триггерных событий PXI, линию локальной шины и линию триггерных событий "точка-точка" PXI (см. [2]). Слоты PXI-1, реализованные в системах PXI Express, также поддерживают локальную шину PXI. Слоты PXI Express обладают возможностью работы с виртуальной локальной шиной, используя преимущества коммутаторов PCI Express, позволяющих одновременно передавать данные между устройствами PCI Express по нескольким путям. Детерминированность движения данных с такой виртуальной локальной шиной может зависеть от коммутатора PCI Express и самих данных.

4.2.3 Новые приборные функции

Возможности системного тактирования и синхронизации в PXI являются ключевым его отличием от других форм-факторов приборов. PXI был создан путем добавления этих функций к шине PCI с высокой пропускной способностью и компактному модульному форм-фактору CompactPCI при сохранении приемлемой стоимости внедрения. Возможности синхронизации и наличие линий триггерных событий PXI сохранены в настоящем стандарте и продолжат использоваться для решения при помощи PXI множества прикладных задач.

С развитием технологий, обеспечивающих более высокую производительность на базе дифференциальных сигналов, и с уже имеющимися дифференциальными соединителями, необходимыми для PCI Express, PXI Express развивает существующие возможности, предоставляя дифференциальный системный тактовый генератор, дифференциальные сигналы синхронизации и дифференциальные сигналы триггерных событий "точка-точка" и сигналы тактового генератора от нового модуля системной синхронизации.

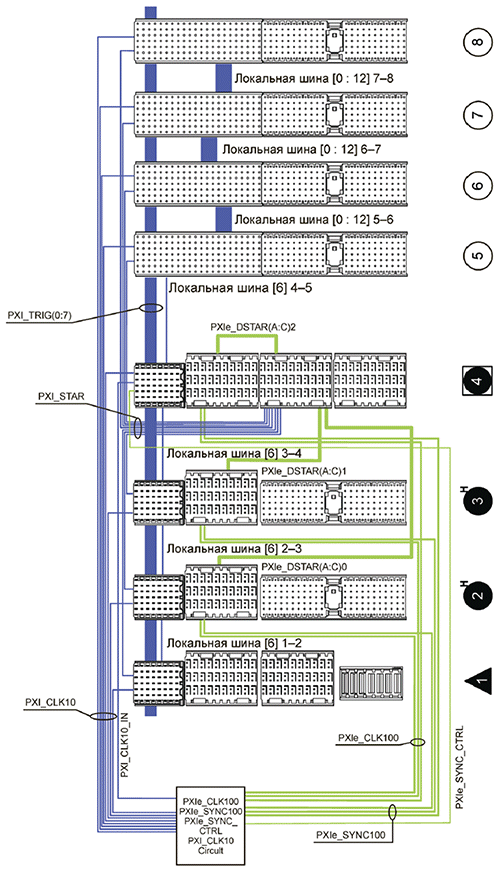

Ключевыми преимуществами обеспечения дифференциального тактирования и синхронизации являются повышенная помехоустойчивость, обеспечиваемая приборным тактовым генератором, и возможность передачи тактовых импульсов с более высокой частотой. Высокая частота тактирования не только обеспечивает более высокую производительность, но также хорошо сочетается с современными процессами и позволяет во многих случаях отказаться от схем умножения частоты в простых модулях. Новые функции добавлены таким образом, чтобы обеспечить совместимость и высокую степень взаимодействия с существующими модулями PXI. В следующих разделах будут описаны новые функциональные возможности. На рисунке 4.19 показан один из примеров подключения сигналов измерительных приборов на кросс-плате PXI Express к слоту системной синхронизации.

|

Примечание - На рисунке указаны названия инструментальных сигналов PXI Express

Рисунок 4.19 - Пример подключения инструментальных сигналов

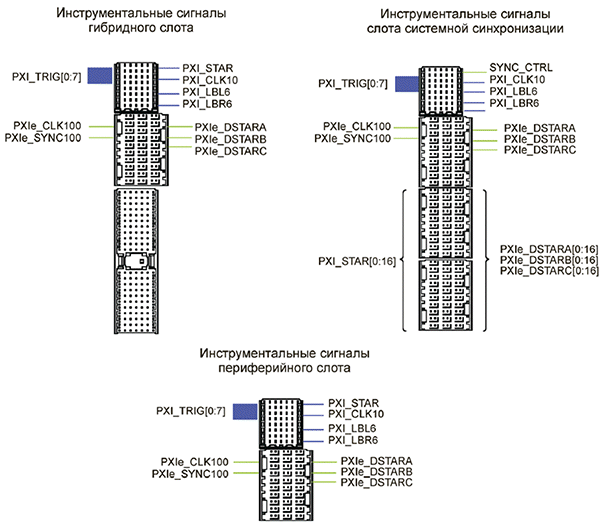

На рисунке 4.20 показано, как расположены инструментальные сигналы на соединителях гибридного слота, периферийного слота PXI Express и слота системной синхронизации.

|

Примечание - Нумерация контактов соединителей приведена в 6.10.

Рисунок 4.20 - Привязка сигналов к соединителям кросс-платы

4.2.3.1 Высокочастотный системный сигнал тактовой частоты

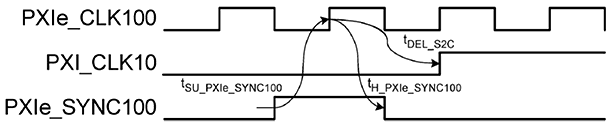

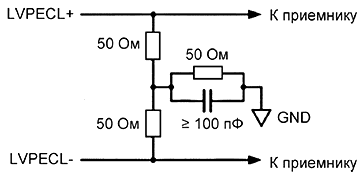

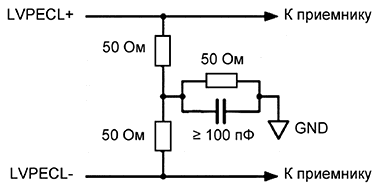

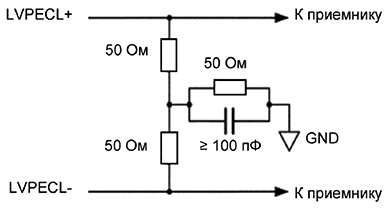

Сигнал высокочастотного системного тактового генератора PXIe_CLK100 является наиболее важным нововведением для синхронизации в PXI Express. Этот дифференциальный тактовый сигнал LVPECL частотой 100 МГц заводится на каждый периферийный слот системы PXI Express. Усовершенствованная технология позволила PXI внедрить дифференциальную синхронизацию, которая обеспечивает повышенную помехоустойчивость кросс-платы. Это позволяет измерительным модулям получать тактовый сигнал с низким джиттером (дрожанием сигнала) и улучшать общую производительность системы. Дифференциальная технология также позволяет использовать более высокую опорную частоту 100 МГц. Это не только обеспечивает более высокую производительность тактирования, но также позволяет снизить стоимость модулей за счет исключения схем умножения частоты для модулей, способных напрямую работать от PXIe_CLK100. PXIe_CLK100 добавлен в настоящий стандарт таким образом, чтобы быть полностью совместимым с PXI_CLK10. PXI_CLK10 и PXIe_CLK100 выровнены по фазе и обеспечивают высокоточную синхронизацию всех устройств, включая совместимые с PXI-1, независимо от того, какую опорную частоту они используют.

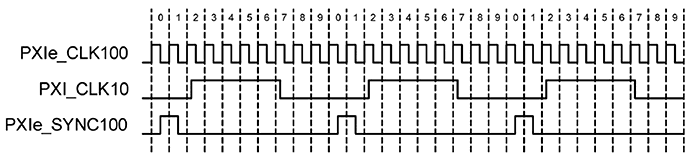

4.2.3.2 Дифференциальный сигнал синхронизации

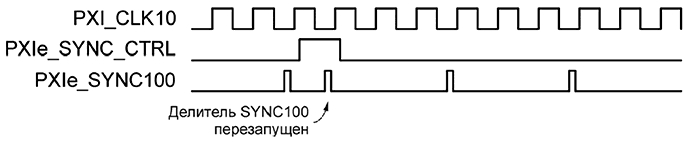

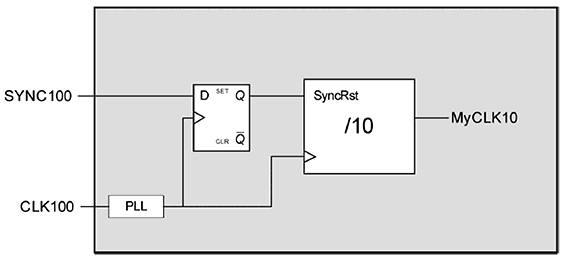

С появлением высокочастотной системной тактовой частоты PXIe_CLK100 возникает необходимость точной синхронизации модулей, использующих этот тактовый сигнал, и модулей, использующих сигнал PXI_CLK10. Дифференциальный сигнал синхронизации PXIe_SYNC100 подводится кросс-платой к каждому модулю и обеспечивает такую возможность. Этот сигнал синхронизирован с PXIe_CLK100 и выдается один раз на каждые 10 тактов PXIe_CLK100, поддерживая фазовое соотношение опорных тактов 10 МГц и 100 МГц. Это ключевой момент для синхронизации и запуска, поскольку он позволяет использовать существующие возможности для запуска и взаимодействия модулей разных типов. Устройства, использующие шину запуска, могут посылать сигналы запуска синхронно с PXI_CLK10 независимо от используемой тактовой частоты. PXIe_SYNC100 также является источником сигнала синхронизации для модулей, использующих опорный сигнал 100 МГц. Это позволяет различным модулям начинать деление тактового сигнала по одному и тому же фронту тактового сигнала, не требуя высокочастотной триггерной шины.

4.2.3.3 Дифференциальные сигналы триггерных событий

Одним из преимуществ PXI является использование для тактирования и синхронизации распространенной логики TTL. Несмотря на то, что логика TTL достаточно эффективна при использовании, она имеет ограничения на максимальное значение частоты сигналов. Благодаря использованию дифференциальных синхросигналов система синхронизации и запуска PXI Express обеспечивает качественные и высокочастотные соединения с каждым модулем. Подобно тому, как PXI_STAR обеспечивает прямое соединение каждого модуля с центральным ресурсом синхронизации, дифференциальные сигналы триггерных событий "точка-точка" PXIe_DSTAR обеспечивают три прямых высокочастотных соединения с модулем системной синхронизации. Ключевым преимуществом этих сигналов является возможность передачи высокочастотных тактовых импульсов к модулям и от модулей в системе PXI. Наличие нескольких соединений позволяет решать большое количество системных задач. Хотя основным назначением PXIe_DSTAR является передача тактовых импульсов, они также могут использоваться и для других задач.

4.2.3.4 Модуль системной синхронизации

Слот 2 или слот линии триггерных событий "точка-точка" в PXI-1 обеспечивает доступ к расширенным приложениям системной синхронизации с индивидуальными подключениями к каждому модулю и возможностью выбора тактового генератора. С добавлением дифференциальных сигналов триггерных событий "точка-точка" и высокочастотного системного опорного тактового генератора в кросс-плате требуется развести большее количество скоростных соединений к модулям. В PXI Express модуль системной синхронизации (STM) является центральной точкой подключения для трех сигналов триггерных событий, добавленных в этом стандарте. Таким образом, STM становится центральной точкой подключения и диспетчером маршрутизации для обеспечения расширенных возможностей системы тактирования и синхронизации в системах PXI Express. Модуль системной синхронизации в системах PXI Express заменяет аналогичный модуль, определенный в PXI-1, при этом оставаясь центральной точкой подключения для линий PXI_STAR и системного тактового генератора на кросс-плате. STM также играет ключевую роль в обеспечении синхронности работы систем, состоящих из нескольких разнородных шасси. Если кросс-плата поддерживает установку STM, то в слот системной синхронизации может быть установлен любой периферийный модуль PXI Express в случае, если в системе отсутствует необходимость в расширенных возможностях синхронизации.

4.2.4 Идентификация слота

В PXI Express имеется аппаратная поддержка географической адресации. Устройство PXI Express может определить номер своего слота, считывая состояние на контактах GA(4:0). Ранее для создания файла pxisys.ini, описывающего топологию системы PXI, менеджеру ресурсов PXI требовалось использовать дерево PCI устройств, файлы chassis.ini и специфическую для производителя информацию о топологии PCI контроллера слота 1. При использовании новой аппаратной поддержки полное дерево шины PCI больше не требуется. Каждый модуль может самостоятельно определить номер своего слота.

4.2.4.1 Драйверы модулей и контакты GA

Чтобы драйверы приборов, VISA и прикладное программное обеспечение смогли находить конкретное устройство по номеру слота, драйвер каждого модуля должен реализовывать алгоритм передачи номера его слота другим программным компонентам в системе. Этот алгоритм определен положениями [3].

4.2.4.2 Определение номера шасси

В отличие от алгоритма определения номера слота модуля, для которого есть аппаратная поддержка в шасси, алгоритм определения номера шасси требует знания номеров шин и устройств коммутаторов PCI Express и модулей в системе. Алгоритм определения номера шасси, в котором находится определенный модуль PXI Express, описан в положениях [4].

4.2.5 Идентификация контроллера

PXI Express обладает аппаратной поддержкой для идентификации шасси PXI Express с помощью EEPROM на шине SMBus. PXI Express также использует информацию о номерах шин соединений от системного модуля к шасси, чтобы установить, какие устройства находятся в каждом шасси. Поэтому положения [4] определяют алгоритм определения того, какие контроллеры существуют, как эти контроллеры получают доступ к SMBus, и какие номера шин подчинены этому контроллеру.

Положения [4] определяют интерфейс для доступа к SMBus с помощью контроллера слота 1. Существует однозначное соответствие между контроллерами слота 1 и экземплярами интерфейса контроллера PXI Express SMBus.

4.2.6 Идентификация шасси

PXI Express использует требования [1] для идентификации кросс-платы и возможностей EEPROM. Системный модуль получает доступ к данному EEPROM через SMBus и дает системе PXI Express возможность однозначно идентифицировать производителя, модель, версию и серийный номер шасси. Он также предоставляет информацию о слотах в шасси и топологии PCI Express. Эта информация может использоваться программным обеспечением для загрузки драйвера шасси для предоставления дополнительной информации о шасси или для доступа к кросс-плате и функциям шасси.

4.2.7 Требования к работоспособности при изменении напряжений питания, токам питания и максимальной потребляемой мощности

Требования к работоспособности при изменении напряжений питания, токам питания и максимальной потребляемой мощности для систем PXI Express включают в себя следующее (см. [1]):

- требования к шинам питания;

- требования к стабилизации напряжений питания;

- требования к пульсации и шумам;

- требования к развязке питающих напряжений;

- требования ко времени нарастания и снятия напряжений питания;

- требования к дополнительным сигналам подсистемы питания, идущим к системному модулю и от него.

PXI Express дополнительно предъявляет требования к минимальному току источника питания шасси на шину напряжения для каждого типа слота. Это обеспечивает высокий уровень взаимодействия между модулями и шасси и предоставляет разработчикам модулей PXI Express информацию относительно тока, ожидаемого от шасси. Требования к питанию для слотов PXI-1, реализованных в системах PXI Express, определены в положениях [2].

4.3 Общие сведения об архитектуре программного обеспечения

PXI Express предоставляет следующие новые программные функции для управления новыми аппаратными ресурсами CompactPCI Express и PXI Express:

- программный интерфейс для доступа к устройствам шасси с последовательным интерфейсом SMBus, таким как EEPROM;

- программный интерфейс запроса номера слота каждого модуля, определяемого выводами GA;

- алгоритм связывания номера шасси с модулями в каждом шасси;

- программный протокол для перечисления компонентов PXI, таких как контроллеры, модули, шасси и прочие ресурсы;

- пространство имен для этих компонентов PXI;

- общий алгоритм регистрации для служб, реализованный драйверами компонентов PXI;

- стандартные программные интерфейсы для сервисов, реализуемых контроллерами, шасси и модулями.

Требуется, чтобы каждый контроллер, шасси и модуль имели собственное программное обеспечение, реализующее и регистрирующее определенные службы (см. [4]). Создавая стандарты для этих служб и способов их регистрации, положения [4] обеспечивают высокий уровень функциональной совместимости. Даже если контроллер, шасси, модуль и библиотека VISA предоставлены разными разработчиками, все нижеперечисленные функции должны работать:

- библиотека VISA должна уметь определять физическое местоположение модуля, взаимодействуя с драйвером модуля;

- драйвер шасси должен уметь управлять ресурсами кросс-платы с помощью шины SMBus на контроллере слота 1;

- конфигурационная программа должна уметь определять перечень шасси и модулей в системе.

Требования к программному обеспечению и функции для PXI Express приведены в положениях [4].

5 Требования к конструкции

В данном разделе определены требования к конструкции систем типа PXI Express. Рассмотрено максимальное количество слотов, расположение системного слота, нумерация слотов, слоты типа PXI-1, требования к шасси, требования к соединителям, типы модулей, совместимость контроллера с шасси, логотип/символы PXI Express, испытания на воздействие окружающей среды и охлаждение.

5.1 Стандарт, используемый для чертежей

Чертежи, содержащиеся в настоящем стандарте, интерпретируются с учетом положений [5].

5.2 Единицы измерения

В настоящем стандарте размеры указаны в миллиметрах, если не указано иное.

5.3 Требования к механическому устройству шасси

Правило. Как и в случае с PXI-1, CompactPCI и CompactPCI Express, в шасси PXI Express необходимо использовать блочный каркас шасси (см. [6]).

5.4 Минимальные требования к слоту для шасси PXI Express

Правило. Для шасси PXI Express необходимо использовать по меньшей мере один периферийный слот PXI Express или один гибридный слот.

Правило. Для шасси PXI Express не используют слот линий триггерных событий "точка-точка", определенный в [2].

Рекомендация. Для шасси PXI Express желательно предусмотреть наличие слота системной синхронизации.

5.5 Характеристики, заимствованные из аппаратного обеспечения PXI

5.5.1 Максимальное количество слотов

Поскольку в положениях [1] предусматривается поддержка 31 слота в соответствии с определением контактов географического адреса, необходимо ограничить максимальное количество слотов в шасси PXI Express до 31 слота.

Правило. Шасси PXI Express не должно иметь более 31 слота.

5.5.2 Требования к системному слоту

Для всех систем, совместимых с PXI Express, требуется кросс-плата/шасси, слот системной синхронизации и, по меньшей мере, один периферийный/гибридный слот PXI Express. Системный слот не является обязательным, если функциональные возможности системного модуля встроены в шасси. Наличие системного слота в шасси позволяет пользователям комбинировать и сравнивать работу разных контроллеров. Однако, поскольку допускается размещение системного слота в любом месте относительно периферийных слотов (см. [1]), существует вероятность возникновения путаницы и несовместимости. Для решения данной проблемы необходимо соблюдать нижеуказанные правила для PXI Express систем.

Правило. Системный слот должен быть крайним левым PXI слотом в шасси/кросс-плате PXI. В документации данный слот считается первым (системным слотом).

Рекомендация. Если ширина системного модуля превышает ширину одного слота, то его следует расширять влево от системного слота в дополнительные слоты расширения контроллера с шагом в один полный слот (размер одного слота составляет 20,32 мм).

Замечание. В системе PXI Express эти дополнительные слоты контроллера предназначены только для физического расширения модуля системного контроллера и не поддерживают периферийные модули. Эти слоты не имеют соединителей, связанных с каналами PCI Express, проложенными на кросс-плате.

Замечание. Расширение системного модуля влево оставляет свободными для пользователя все периферийные слоты PXI Express.

Рекомендация. Системный модуль не следует расширять вправо от системного слота в периферийные слоты.

Замечание. При расширении системного модуля вправо количество доступных пользователю периферийных слотов PXI Express может уменьшиться.

Правило. Для каждого системного модуля PXI Express необходимо документировать, сколько слотов расширения контроллера (слева от системного слота) и периферийных слотов он занимает.

Правило. Для каждого шасси PXI Express необходимо документировать количество доступных слотов расширения периферийных устройств и контроллеров.

Замечание. Два предыдущих правила помогают конечным пользователям определить, совместим ли определенный контроллер с определенным шасси и количество доступных периферийных слотов шасси.

На рисунке 4.17 показаны типовые обозначения слотов расширения системы в системе PXI Express.

5.5.3 Нумерация и ориентация слотов

Нумерация слотов шасси PXI Express осуществляется согласно правилам (см. [2]), за исключением того, что PXI Express допускает существование шасси со встроенным системным модулем.

Правило. Шасси PXI Express с системным слотом должно соответствовать требованиям к нумерации слотов (см. [2]).

Правило. Шасси PXI Express без системного слота (встроенный системный модуль) должны соответствовать требованиям к нумерации слотов (см. [2]), за исключением того, что нумерация слотов начинается с 2.

Разрешение. Ориентация слотов и схемы нумерации могут отличаться от определенных в PXI-1, если они понятны и логичны для конечного пользователя.

5.5.4 Слот PXI-1

В шасси PXI Express могут быть слоты, поддерживающие платы PXI, которые соответствуют требованиям положений [2]. Эти слоты соответствуют требованиям положений [2] к конструкции и называются слотами PXI-1.

Разрешение. Периферийные модули и слоты PXI-1 3U и 6U могут использоваться в системах PXI Express.

Правило. Слоты PXI-1 в шасси PXI Express должны соответствовать требованиям к конструкции, установленным в положениях [2].

Правило. Периферийные модули PXI-1 не должны подключаться к слотам гибридных периферийных устройств, если только они не соответствуют требованиям к модулям PXI-1, совместимым с гибридными слотами, как это определено в настоящем стандарте.

Рекомендация. Периферийные модули PXI-1 3U и 6U должны соответствовать рекомендациям положений [1] по высоте компонентов стороны 2, чтобы свести к минимуму проблемы с конструктивной совместимостью.

5.5.5 Периферийные модули, совместимые с гибридными слотами

PXI-1 или соответствующий ECN определяет совместимый с гибридным слотом периферийный модуль PXI-1 3U и 6U, который состоит из модуля PXI-1 3U или 6U, в котором соединитель J2 HM заменен на соединитель eHM. Соединитель eHM устанавливается в верхние восемь колонок соединителя J2 PXI-1 и представляет собой модифицированный соединитель HM с шагом контактов 2 мм со специальным позиционирующим ключом. Этот тип платы может использоваться в любом гибридном слоте PXI-1 или PXI Express.

Замечание. Периферийный модуль PXI-1, совместимый с гибридным слотом, может использоваться в традиционном гибридном слоте PXI-1 или гибридном слоте PXI Express.

5.6 Функции, заимствованные из CompactPCI Express

Так же, как PXI-1 основан на CompactPCI, PXI Express основан на CompactPCI Express, который интегрировал PCI Express в архитектуру типа CompactPCI. В данном разделе приведено описание правил, замечаний, разрешений и наблюдений (см. [1]).

Правило. Все требования к конструкции (см. [1]) должны выполняться, если в настоящем стандарте не указано иное.

5.6.1 Требования к соединителям модуля

5.6.1.1 Соединитель типа ADF

Правило. Модули PXI Express должны использовать соединитель ADF-F-3-10-2-F-25 (см. [1]).

5.6.1.2 Соединитель типа eHM

Правило. Модули PXI Express должны использовать соединитель eHM-F2 (см. [1]).

5.6.1.3 Соединитель типа UPM

Правило. Модули системного контроллера должны использовать соединитель UPM-M-7 или UPM-M-7-HP (см. [1]).

5.6.2 Требования к соединителю кросс-платы

5.6.2.1 Соединитель типа ADF

Правило. Слоты PXI Express должны использовать соединитель ADF-M-3-10-2-B-25 или ADF-M-3-10-2-S-25-0100 (см. [1]).

5.6.2.2 Соединитель типа eHM

Правило. Слоты PXI Express должны использовать соединитель eHM-M2-HP или eHM-M2 (см. [1]).

5.6.2.3 Соединитель типа UPM

Правило. Слоты системного контроллера должны использовать соединитель UPM-F-7 (см. [1]).

5.6.3 Требования к модулям 3U и 6U

5.6.3.1 Системный модуль

Правило. Модули PXI Express 3U и 6U должны соответствовать требованиям к конструкции (см. [1]).

Замечание. Модули и объединительные платы системы 6U PXI Express могут использовать соединители J3/P3, J4/P4 и J5/P5, если это необходимо для ввода-вывода на задней панели.

5.6.3.2 Периферийный модуль PXI Express

Правило. Периферийные модули 3U PXI Express должны соответствовать требованиям к конструкции периферийного модуля 3U типа 2, приведенным в положениях [1].

Правило. Периферийные модули 6U PXI Express должны соответствовать требованиям к конструкции периферийных плат 6U типа 2 (см. [1]), за исключением того, что не должны использоваться соединители J3/J4/J5. Печатная плата периферийного модуля 6U PXI Express должна соответствовать требованиям, приведенным на рисунке 5.1.

Правило. Периферийные модули 6U PXI Express, которые не являются модулями системной синхронизации 6U, не должны оснащаться какими-либо соединителями, кроме соединителей XJ3, XJ4 и XJ8.

Разрешение. На периферийные модули 6U PXI Express может устанавливаться опциональный соединитель eHM в положение XJ8, как показано на рисунке 5.2, когда требуется дополнительное питание.

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.1 - Печатная плата периферийного модуля 6U PXI Express

|

Рисунок 5.2 - Периферийный модуль PXI Express 6U

5.6.4 Требования к кросс-плате

Правило. Кросс-платы PXI Express 3U и 6U в части размера, отверстий механического монтажа и допусков должны соответствовать требованиям положений [1].

Более подробное описание требований к расположению различных соединителей приведено в следующих разделах.

5.6.4.1 Системный слот

Правило. Системные слоты PXI Express 3U и 6U должны соответствовать требованиям к конструкции (см. [1]).

Разрешение. Как и в CompactPCI Express, системные слоты 6U могут использовать соединители J3/J4/J5, если это необходимо для ввода-вывода на задней панели.

5.6.4.2 Периферийный слот

Правило. Периферийные слоты 3U PXI Express должны соответствовать требованиям к конструкции для периферийных слотов 3U типа 2 (см. [1]).

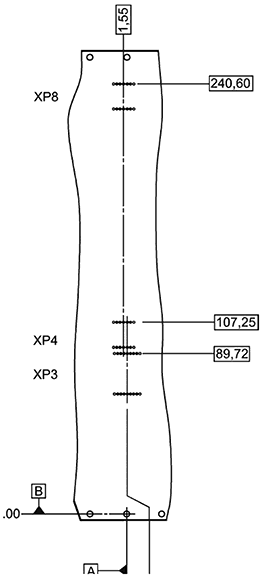

Правило. Периферийные слоты 6U PXI Express должны соответствовать требованиям к конструкции для периферийных слотов 6U типа 2 (см. [1]), за исключением того, что дополнительный соединитель XP8 eHM должен быть установлен на месте, указанном на рисунке 5.3.

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.3 - Периферийный слот PXI Express 6U

5.6.4.3 Гибридный периферийный слот PXI Express

Правило. Гибридные периферийные слоты 3U PXI Express должны соответствовать требованиям к конструкции гибридных периферийных слотов 3U (см. [1]).

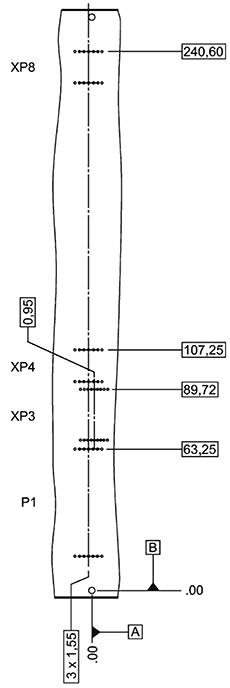

Правило. Гибридные периферийные слоты PXI Express 6U должны соответствовать требованиям к конструкции гибридных периферийных слотов 6U (см. [1]), за исключением того, что соединитель XP8 eHM должен быть установлен в положение, показанное на рисунке 5.4, а традиционные соединители P3/P4/P5 не должны использоваться.

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.4 - Гибридный слот PXI Express 6U

5.7 Новые типы модулей и слотов

5.7.1 Требования к модулю системной синхронизации PXI Express

Правило. Модули системной синхронизации 3U PXI Express должны соответствовать требованиям к конструкции, приведенным на рисунке 5.5.

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.5 - Печатная плата модуля системной синхронизации 3U PXI Express

Правило. Печатные платы модуля системной синхронизации 6U PXI Express должны соответствовать требованиям к конструкции, приведенным на рисунке 5.6.

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.6 - Печатная плата системного модуля синхронизации PXI Express 6U

Разрешение. Модуль системной синхронизации 6U в формате PXI Express может содержать соединители TJ5 и TJ6, что позволяет использовать его в шасси, для которого требуется, чтобы такой модуль обеспечивал достаточное количество линий триггерных событий "точка-точка" или дифференциальных сигналов триггерных событий, или в шасси с поддержкой установки модулей системной синхронизации 3U.

5.7.2 Требования к кросс-плате для новых типов слотов

Правило. Кросс-платы PXI Express 3U и 6U должны соответствовать требованиям в части размера, отверстий механического монтажа и допусков (см. [1]).

Более подробное описание требований к расположению различных соединителей приведено в следующих разделах.

5.7.2.1 Требования к слотам системной синхронизации PXI Express

Правило. Слоты системной синхронизации 3U PXI Express должны соответствовать требованиям к конструкции, приведенным на рисунке 5.7.

Правило. Слоты системной синхронизации 6U PXI Express должны соответствовать требованиям к конструкции, приведенным на рисунке 5.8.

Правило. Слоты системной синхронизации 6U PXI Express, которые поддерживают установку модулей системной синхронизации 3U, должны соответствовать требованиям к конструкции, приведенным на рисунке 5.9.

Правило. Если в слоте системной синхронизации не используется соединитель TP1, то на кросс-плате в зоне расположения TP1 максимальная высота компонентов не должна превышать 2,2 мм, чтобы избежать проблем с конструктивной совместимостью с модулями системной синхронизации с установленным соединителем TJ1.

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.7 - Размеры кросс-платы для слота системной синхронизации 3U PXI Express

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.8 - Размеры кросс-платы для слота системной синхронизации 6U PXI Express

|

Примечания

1 Детали расположения соединителя с учетом положений [1].

3 Все остальные требования к конструкции с учетом положений [1].

Рисунок 5.9 - Размеры кросс-платы для слота системной синхронизации PXI Express 6U с поддержкой установки модулей 3U

Правило. Для областей применения, где соединитель TP1 кросс-платы является необязательным, на кросс-плате в зоне расположения TP1 максимальная высота компонентов не должна превышать 2,2 мм, чтобы избежать проблем с конструктивной совместимостью с модулями системной синхронизации с установленным соединителем TJ1.

Разрешение. Если кросс-плата 3U PXI Express может соединить все слоты, которые могут подключаться к линиям триггерных событий "точка-точка" и дифференциальным сигналам триггерных событий через соединитель TP2, соединитель TP1 может не использоваться.

Разрешение. Кросс-плата 6U PXI Express, обеспечивающая достаточное количество дифференциальных сигналов триггерных событий и линий триггерных событий "точка-точка" для всех слотов, которые могут к ним подключаться, может поддерживать либо установку двух модулей системной синхронизации 3U, либо модуля системной синхронизации 6U с дополнительными соединителями. Если такая кросс-плата 6U PXI Express способна соединить все слоты, которые могут подключаться к линиям триггерных событий "точка-точка" и дифференциальным сигналам триггерных событий, без использования соединителя TP5, соединитель TP5 может не использоваться.

5.8 Требования для установки модулей 3U в слоты 6U

Как и PXI-1, PXI Express позволяет эффективно использовать модули 3U в шасси 6U.

С механической точки зрения такая конфигурация может быть реализована за счет использования центральных выступов, закрепленных внутри шасси, для физической поддержки вставки, извлечения и монтажа нижних и верхних модулей 3U, находящихся в слоте 6U. В качестве альтернативы это может быть выполнено механическим образом с помощью адаптера (переходника) для установки, прикрепленного на двух модулях 3U перед установкой в слот 6U. На рисунке 4.18 показан пример шасси 6U с поддержкой установки модулей 3U.

Правило. Шасси 6U PXI Express, которые поддерживают установку модулей 3U, должны иметь соответствующие соединители в нижней половине слота 6U для реализации нижнего слота 3U в соответствии с типом реализуемого слота 3U (системный, гибридный, периферийный PXI Express, PXI-1 или слот временной синхронизации системы).

Правило. Шасси 6U PXI Express, поддерживающие установку модулей 3U, должны иметь соответствующие соединители в верхней половине слота 6U для реализации верхнего слота 3U в соответствии с типом реализуемого слота 3U (гибридный, периферийный PXI Express, PXI-1 или слот временной синхронизации системы).

Правило. В таблице 5.1 показаны варианты использования верхнего слота 3U в зависимости от того, как использован нижний слот 3U в слоте 6U шасси PXI Express с поддержкой установки модулей 3U.

Таблица 5.1 - Реализация верхнего и нижнего слота 3U

Нижний слот 3U | Верхний слот 3U | ||||

Система | Периферия PXIe | Системная синхронизация | Гибридная периферия | Периферия PXI 2.X | |

Система | Нет | Да | Нет | Да | Да |

Периферия PXIe | Нет | Да | Нет | Да | Нет |

Системная синхронизация | Нет | Да | Да | Нет | Нет |

Гибридная периферия | Нет | Да | Нет | Да | Нет |

Периферия PXI 2.X | Нет | Да | Нет | Да | Да |

Замечание. Верхний слот системной синхронизации 3U не разрешено располагать над любым другим слотом, кроме нижнего слота системной синхронизации 3U.

Замечание. Запрещается использовать в качестве системных верхние слоты 3U.

Замечание. Нижний слот, который является периферийным слотом PXI Express, слотом системной синхронизации или гибридным периферийным слотом не предназначен для расположения периферийного слота PXI-1 в верхнем положении. Это сделано для того, чтобы модуль 6U с верхним соединителем eHM для дополнительного питания мог иметь возможность подключения к слоту 6U, поддерживающему установку модулей 3U.

5.9 Логотип PXI

На продуктах PXI Express используется тот же логотип, что и на продуктах PXI. Периферийные модули PXI Express, системные модули PXI Express, модули системной синхронизации PXI Express и шасси PXI Express могут содержать логотип PXI Express в своих маркетинговых материалах, технических описаниях и руководствах, чтобы помочь клиентам определить, что продукты PXI поддерживают возможности PCI Express.

Разрешение. Разработчики, являющиеся членами альянса PXI Systems, могут использовать логотип PXI, как определено ниже, либо на передней панели, либо на рукоятке инжектора/эжектора продуктов, заявляя о полном соответствии положениям настоящего стандарта.

Правило. Если используется логотип PXI, разработчик должен получить лицензию на использование логотипа торгового знака от альянса PXI System.

Правило. Если используется логотип PXI, он не должен быть изменен каким-либо образом, за исключением его масштабирования. Логотип не должен содержать каких-либо дополнений.

На рисунке 5.10 показан логотип PXI. Члены альянса PXI Systems могут получить логотип и лицензию от альянса.

Рисунок 5.10 - Логотип PXI

Правило. Разработчики, являющиеся членами альянса PXI Systems, не должны использовать логотип PXI Express, как определено ниже, на какой-либо части аппаратных продуктов PXI или PXI Express.

Разрешение. Разработчики, являющиеся членами альянса PXI Systems, могут использовать логотип PXI Express, как определено ниже, в маркетинговых материалах, технических описаниях и руководствах по периферийным модулям PXI Express, системным модулям PXI Express, модулям системной синхронизации PXI Express и шасси PXI Express, заявляя о полном соответствии положениям настоящего стандарта.

Правило. Если используется логотип PXI Express, разработчик должен получить лицензию на использование логотипа торгового знака от альянса PXI System.

Правило. Если используется логотип PXI Express, он не должен быть изменен каким-либо образом, за исключением масштабирования. Логотип не должен содержать каких-либо дополнений.

На рисунке 5.11 показан логотип PXI Express. Члены альянса PXI Systems могут получить логотип и лицензию от альянса.

|

Рисунок 5.11 - Логотип PXI Express

5.10 Шасси со встроенными системными модулями

Разрешение. Шасси PXI Express может быть выполнено со встроенным системным модулем и, следовательно, без системного слота.

5.11 Требования к охлаждению

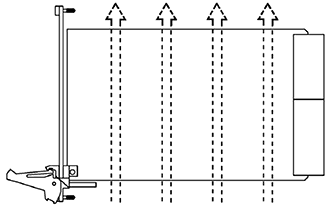

5.11.1 Требования к охлаждению модуля

Правило. Модули должны быть сконструированы таким образом, чтобы обеспечить необходимый путь воздушного потока от нижней к верхней части модуля, как показано на рисунке 5.12.

Замечание. Поток воздуха и, следовательно, охлаждение через модуль зависит как от корпуса, так и от конструкции модуля. Модули с более низким сопротивлением воздушному потоку получат больший воздушный поток, а модули с более высоким сопротивлением получат меньший воздушный поток для данного шасси.

|

Рисунок 5.12 - Направление потока охлаждающего воздуха в системе PXI Express

Правило. Производители модулей должны оформлять документально и предоставлять заказчику номинальную и пиковую мощность, рассеиваемую модулем по шине питания при нормальных условиях эксплуатации.

Рекомендация. Одинарные модули 3U не должны рассеивать внутри шасси мощность более 30 Вт.

Рекомендация. Одинарные модули 6U не должны рассеивать внутри шасси мощность более 60 Вт.

Замечание. Для шасси 6U обычно требуется больший поток воздуха на слот, чем для шасси 3U, при заданной температуре окружающей среды из-за эффектов предварительного нагрева.

Рекомендация. Модулям желательно иметь возможность обнаружения превышения температуры их компонентов пределов предполагаемого использования и возможность принять меры для того, чтобы вернуть температуру компонентов в рабочий диапазон.

Замечание. Действия, направленные на возврат температуры в рабочий диапазон, могут заключаться в отключении всего модуля или его части таким образом, чтобы модуль не функционировал до перезапуска системы. Также допускаются и иные меры.

5.11.2 Требования к охлаждению шасси

Правило. Шасси должно обеспечивать принудительный обдув модулей снизу вверх, как показано на рисунке 5.12.

Замечание. Для типовых конфигураций шасси воздушный поток через слот будет проходить против силы тяжести или вверх (т.е. аналогично подъему нагретого воздуха естественным путем). Однако в настоящем стандарте не исключаются другие ориентации модуля, например, горизонтальная.

Правило. Производители шасси должны оформлять документально и предоставлять заказчику максимальную общую мощность, которую данное шасси может рассеять в пределах системы, а также максимальную мощность, которую оно может рассеивать для своего наихудшего слота. Кроме того, изготовитель должен оформить документально и предоставить заказчику конкретную процедуру испытаний, используемую для определения этих уровней рассеивания мощности.

Рекомендация. Значение рассеиваемой мощности слота для наихудшего случая следует основывать на доступной мощности для данного слота и на возможностях охлаждения шасси для слота в наихудшем случае.

Рекомендация. Карты тепловой нагрузки следует использовать во всех слотах шасси при определении возможностей охлаждения для шасси и наихудшего варианта для слота.

Правило. Шасси PXI должно содержать панели-заглушки, установленные в слотах, в которых не установлены модули.

Замечание. Если панели-заглушки не установлены в слоты, в которых отсутствуют модули, надлежащее охлаждение модуля не гарантируется.

5.12 Требования к внешним и климатическим воздействиям

Рекомендация. Перечисленные ниже испытания следует проводить в соответствии с методиками, определенными в [7].

Правило. Результаты испытаний и отчеты по работе в климатических условиях должны быть доступны конечным пользователям систем PXI Express. Все производители шасси и модулей PXI Express должны предоставлять характеристики внешних и климатических воздействий, при которых обеспечивается работоспособность своей продукции, как описано ниже.

Рекомендация. Всем производителям следует указывать требуемые характеристики, как описано ниже, в технических описаниях своей продукции.

Правило. Если изготовитель принимает решение использовать методики испытаний, отличные от рекомендованных выше, эти методики, в дополнение к результатам испытаний и отчетам, должны быть оформлены документально и предоставлены заказчику.

Замечание. Производитель системы несет ответственность за выбор модулей и шасси, соответствующих требованиям к внешним и климатическим воздействиям для области применения.

5.12.1 Температурные характеристики

Правило. Шасси и модули PXI должны быть испытаны на работу в диапазоне температур хранения и эксплуатации.

5.12.2 Характеристики влажности

Рекомендация. Шасси и модули PXI Express следует проверять на стойкость к влажности.

5.12.3 Характеристики вибрационных воздействий

Рекомендация. Шасси и модули PXI Express следует испытывать на стойкость и живучесть к вибрационным воздействиям.

5.12.4 Характеристики акустического шума

Рекомендация. Все шасси PXI Express следует испытывать на уровни акустического шума (уровень звукового давления, взвешенный по шкале А, LPA). Данные акустические испытания следует проводить по ГОСТ Р 53032 на стандартном испытательном стенде на рабочем месте оператора. Испытание шасси следует проводить на шасси, работающем при полной нагрузке, с установленными передними панелями. Если доступно несколько вариантов скорости вентилятора, должны быть указаны уровни звукового давления для различных вариантов частоты вращения вентилятора.

Замечание. Может быть предоставлен взвешенный по шкале А уровень звуковой мощности. Данные акустические испытания следует проводить по ГОСТ Р 53032 на стандартном испытательном стенде.

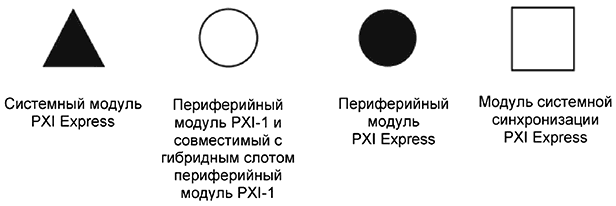

5.13 Символы совместимости PXI Express

5.13.1 Символы модуля

Правило. Символ совместимости системного модуля PXI Express, показанный на рисунке 5.13, должен быть виден на передних панелях модулей системы PXI Express.

Правило. Символ совместимости периферийных модулей PXI Express, показанный на рисунке 5.13, должен быть виден на передних панелях периферийных модулей PXI Express.

Правило. Символ совместимости модуля системной синхронизации PXI Express, показанный на рисунке 5.13, должен быть виден на передних панелях модулей системной синхронизации PXI Express.

Замечание. Модули PXI-1 и совместимые с гибридным слотом модули PXI-1 имеют видимые символы периферийных модулей (см. [2]).

|

Рисунок 5.13 - Символы модуля

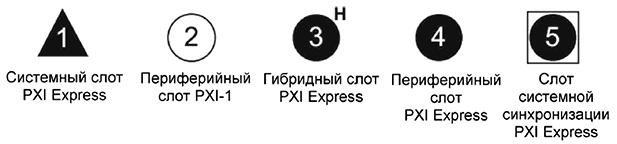

5.13.2 Символы слотов шасси

Правило. Символ совместимости системного слота PXI Express, показанный на рисунке 5.14, должен быть виден непосредственно под системным слотом PXI Express на шасси PXI Express с номером слота, указанным внутри символа.

Правило. Символ совместимости с периферийными слотами PXI Express, показанный на рисунке 5.14, должен быть виден непосредственно под периферийными слотами PXI Express на шасси PXI Express с номером слота, указанным внутри символа.

Правило. Символ совместимости с гибридным слотом PXI Express, показанный на рисунке 5.14, должен быть виден непосредственно под гибридными слотами PXI Express на шасси PXI Express с номером слота, указанным внутри символа.

Правило. Символ совместимости слота системной синхронизации PXI Express, показанный на рисунке 5.14, должен быть виден непосредственно под слотом системной синхронизации PXI Express на шасси PXI Express с номером слота, указанным внутри символа.

Замечание. Слоты PXI-1 имеют видимый символ периферийного слота (см. [2]).

|

Рисунок 5.14 - Символы слотов

6 Требования к электрическим характеристикам

В данном разделе приводятся подробные требования к электрическим характеристикам для разработки PXI Express-совместимых периферийных модулей, системных модулей, модулей системной синхронизации и кросс-плат. Также рассматриваются соответствующие контакты соединителей, требования к источнику питания и вопросы реализации форм-фактора 6U.

6.1 Сигналы PCI

Кросс-платы PXI Express могут содержать гибридные слоты или слоты PXI-1. Такие слоты содержат контакты для функций PCI (см. [2] и [6]).

6.1.1 Требования к гибридному слоту

Правило. Гибридные слоты в кросс-платах PXI Express должны соответствовать положениям для сигналов на соединителе P1 (см. [2]).

Правило. Для гибридных слотов должна использоваться адресная строка для привязки сигнала IDSEL на основе номера логического слота (см. [6]).

Правило. Для гибридных слотов должны использоваться назначения прерываний на основе номера логического слота (см. [6]).

6.1.2 Требования к слоту PXI-1

Правило. Слоты PXI-1 в кросс-платах PXI Express должны соответствовать положениям для сигналов на соединителях P1 и P2 (см. [2]).

Правило. Для слотов PXI-1 должна использоваться адресная строка для отображения привязки сигнала IDSEL на основе номера логического слота (см. [1]).

Правило. Для слотов PXI-1 должны использоваться назначения прерываний, основанные на номере логического слота (см. [6]).

6.2 Сигналы CPCI Express

Сигналы, участвующие в обмене данными PCI Express, а также различные вспомогательные сигналы, используемые модулями и слотами PXI Express, определены положениями [1]. Разработчикам PXI Express необходимо следовать требованиям настоящего стандарта при разработке объединительных плат и модулей PXI Express (см. также [1]).